У него для Малины есть переходник

https://goo.gl/images/6xW3b8

https://goo.gl/images/zLUAdC

https://goo.gl/images/xppXaN

Да, Герман, спасибо. Вчера понял это. Кристеки сразу покупать буду - уже немного изменил заказ у iancanada. Pulsar-ы, конечно, нехило стоят, по 400 евро (их 2 штуки нужно).

Спасибо за инфо по ним - буду разбираться, это уже не уровень импульсивной покупки.

Для музыки. У меня ЦАП DSD Sygnalyst DSC 2.7, он только с потоком DSD работает. Сейчас использую Advanced Amanero, хочу попробовать вывод DSD Native через I2S BBB. Насколько удалось разобраться - BBB с драйвером Botic от Miero это единственный SoC, способный на вывод DSD512 по I2S.

Ну у него и подход ультимативный - сначала буферизация сигнала, потом изоляция и реклок. Аналогичное решение (Cronus + Hermes от twistedpearaudio) стоит на 20% дешевле, но, по моему мнению, реализация iancanada заметно более продвинута.

У Wired Botox еще дешевле, правда схема другая  . Совсем удешевлённый вариант.

. Совсем удешевлённый вариант.

Остаётся или 502DAC или Botox. Хотя и хвалят предпоследний, схема у него довольно простая, а сравнения так и не сделали  .

.

А что значат вот эти Ваши лошадки, мячики? Зачем всё это?

Это детский сад

Не всегда срабатывает кнопка “ответить”. Приходится повторять!

По себе не судят  !

!

Сужу по тебе, дружище!

У меня уже пару лет есть такой. На DSC - хуже Аманеро, по следующим причинам:

- Нет линии MUTE (в Аманеро есть) - сильные щелчки при переключении треков и режима PCM-DSD.

- Изолятор без последующего реклока - увеличение джиттера.

К сожалению, этот интерфейс проиграл даже обычному Аманеро по этим причинам на DSC (на ЦАПах с реклоком входных сигналов - нет).

Тем более Advanced Аманеро (на Кристеках и раздельным питанием 6 линий), которое я сейчас использую.

На сейчас мне кажется очень перспективным подход BBB (I2S) - FIFO/изолятор/реклок - DSC. Дополнительный бонус - отсутствие шумов пакетизации USB (гармоники 8кГц).

сильные щелчки при переключении треков и режима PCM-DSD.

Если вы используете воспроизведение одного формата, например, DSD512 (т.е. все конвертируете в DSD512 перед подачей на usb вход конвертера), то никаких щелчков нет.

Изолятор без последующего реклока - увеличение джиттера.

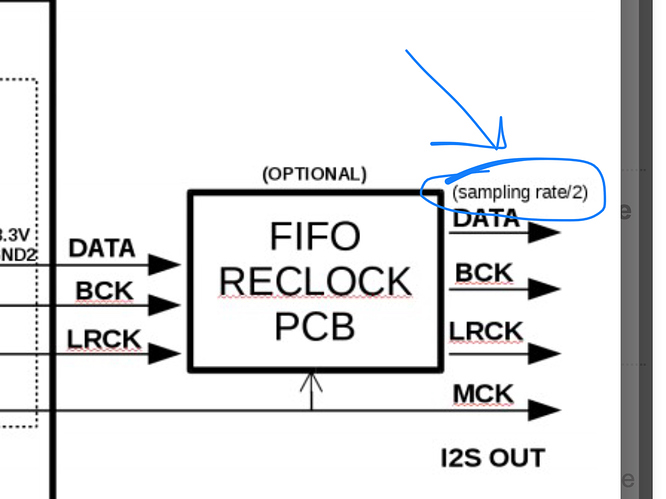

FIFO реклок там имеется в виде опции внешний, но с уменьшением вдвое выходной частоты дискретизации, т.е. для выход DSD512 придется подавать на вход DSD1024 (конвертер это поддерживает, также как и HQPlayer)  .

.

вероятно старая версия .

это новый XMOS 768K+FIFO reclock PCB

На версии по вашей ссылке нет реклока. Только изолятор. Именно эта версия у меня. Она давно появилась.

У них есть отдельная плата FIFO, но там сильные ограничения по частоте (PCM 192К, если не путаю). Мне это не подходит.

Если речь об этой опции

http://www.diyinhk.com/shop/audio-kits/132-fifo-reclock-jitter-eliminator.html

То

The drawback of this reclock appoach is reduced maximum sampling rate. For our 384k xmos PCB, the maximum sampling rate will become 192k PCM. For our 768k xmos PCB, the maximum sampling rate will also become 192k PCM if no modification was done(When /R2 is cut and /R1 is short, the maximum sampling rate after reclock is 384k

Далеко не факт, что потянет DSD512.

И реклок там не уменьшает частоту дискретизации, просто его скорости не достаточно для больших частот. Поэтому и появляется ограничение.

Далеко не факт, что потянет DSD512.

И реклок там не уменьшает частоту дискретизации, просто его скорости не достаточно для больших частот. Поэтому и появляется ограничение.

К тому же всегда можно пообщаться с автором (он немногословен, но всегда отвечает на вопросы  ).

).

Да, может и потянуть. Нет данных. Поэтому и не нравится.

Загадочное примечание SamplingRate/2 мне не понятно. Если частота уменьшается в 2 раза на линии DATA, то как, например, после этого буфера будет PCM воспроизводиться, BCK, LRCK - со старой частотой, DATA с уменьшенной. Если подать PCM 24bit на вход, 48bit на выходе будет (фронтBCK два раза пройдут по одному отсчету DATA). Фрейм PCM развалится к черту.

UPDATE

Кстати не факт, что после этого FIFO вообще можно будет DSD Native получить. В DSD Native 2 линии данных D1 и D2, по линиям DATA и LRCK. Т.е. нужна буферизация и на LRCK. Ее, очевидно, нет. Поэтому diyinhk в описании буфера ничего о DSD не говорит.

Но это тоже догадка. Проще задать вопрос производителю.

sampling rate/2 разумеется относится ко всем сигналам на выходе, по другому просто смешно  .

.

И реклок там не уменьшает частоту дискретизации, просто его скорости не достаточно для больших частот. Поэтому и появляется ограничение.

Тоже смешно, особенно «его скорости не достаточно для больших частот»  (это для триггера шмитта, который используется в схеме). И очевидное преимущество такой схемы есть в описании:

(это для триггера шмитта, который используется в схеме). И очевидное преимущество такой схемы есть в описании:

The MCK from the I2S input is used to drive the input flip flop for FIFO reclock, it do not have the problem as the other complex reclock scheme which drop or double dozens of unnecessary samples every second, and it do not use CPLD/FPGA as the other design which actually increase the jitter tenth of time after reclock. This PCB is target for audiophile.

И этот реклокер можно использовать для DSD:

Вопрос:

Do I need FIFO Reclock Jitter Eliminator if I playback DSD files only by Isolated XMOS 768kHz DXD DSD512(DSD1024) high-quality USB to I2S/DSD PCB?

Ответ автора:

You can compare the different. FIFO Reclock Jitter Eliminator can be used.

Рад, что повеселил. Так редко удается добро людям сделать. Не любая микросхема может работать на 40-50МГц (MCK для DSD512).

Если все частоты уменьшаются в 2 раза, то разрешите плс противоречие, не понимаю:

- на на входе имеем DATA, BCK, LRCK PCM 24 bit. 88К, например. Т.е. по линии DATA идут 24 бита левого/правого канала c частотой 2 * 24 * 88К. LRCK = 2 * 88К.

- на выходе устройства все частоты уменьшаются в два раза (вы утверждаете), DATA остается 24 бита, но становится 44К с частотой 2 * 24 * 44К, LRCK = 2 * 44К.

Вопрос - это FIFO буфер с flip-flop или аппаратный даунсемплер?