Насколько я понимаю, Джиттер актуален для PCM, а не для DSD.

Нет. Везде важен.

Фазовое дрожание фронтов входного DSD сигнала естественно влияет на звуковой результат.

Вы имели ввиду фронтов CLK сигнала?

Да. CLK считаю составной частью DSD сигнала.

CLK должен быть эталонным.

К DATA требования помягче. Лишь бы не размазывались на четверть периода CLK.

MusicScope имеет требуемый функционал для количественных измерений. На сайте производителя выложены файлы J-test (в pcm).

В свете последних рассуждений о точности резисторов, FPGA, “токовом подходе” и.т.д. мне показалось интересным аналитически (я физик-теоретик по образованию) рассмотреть вопрос восстановления сигнала в DSC.

Свои мысли на эту тему я оформил в данном файле. Основная цель - систематизировать свои представления о функционировании DSC.

Буду признателен за обратную связь/дополнения.

Для токового выхода так считается -

Допустим, у нас резисторы 4,7К, их 32 штуки, при “1” на всех, и при “0” на противоположном плече максимальный Imax=5//(24700/32)= 0.017А, т.е 17мА, это пик ту пик, т.е. 8,5мА амплитудного, или 6мА RMS

При резисторе, на котором выделяется сигнал 70Ом Ua=0.00670=0.42В.

При трансформаторе 1:5 выход 2,1В.

Это без ограничений стандарта. На практике получается 1,3В 0дБ.

Можно добиться увеличения точности восстановления путем использования

высокоточных резисторов для первых и последних 5-6 резисторов в наборе из 32

установив резисторы, например, с точностью 0,01%.

Как так то?

Для дифф схемы вроде как:

Imax=5/(4700/32)= 0.034мА !? т.к. в макс размахе одно плечо = 5В другое 0.

А куда денутся резисторы того плеча, которое на ноль?

Они последовательно, 4,7К на плюс и 4,7 на ноль, итого 9,6К/32

Все правильно, Алексей… все правильно.

У 28 параллельно соединенных сопротивление вероятность отклонения от средней ожидаемой точки гораздо ниже, чем у одного или двух.

Так же, если сделать первые 4 резистораочень точными (которые по стандартам DSD всегда будут находится в 0 и/или в 1) , то каждый последующий резистор, не сильно повлияет на отклонение от ожидаемой средней точки.

Мой поклон, Виталий.

Очень интересно и, очень точно по каждому пункту.

Даже не знаю что добавить.

Тема сигнальных трансформаторов осталась немного за кадром, которые, как мне кажется, являются неразрывным целым “в этой концепции”. Но, тему трансформаторов так просто разложить по полочкам, как у тебя это получилось с DSC, не получится.

Так этот пример был для мной предложенного алгоритма а не для 595?

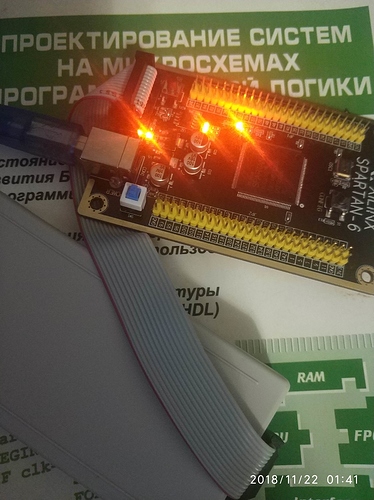

Кручу верчу проект на ПЛИС, дело движется. Раньше работал с Actel, а этот проект будет в Xilinx spartan-6

Нужна обратная связь.

- Делать ли хардварный вход в ПЛИС для установки ширины резистивной матрицы 8-16-32бит). Не используемые биты резисторов хочу в Z состояние ставить. Это для тестов только.

- Реклок в ПЛИСе целесообразен?!

Делается расчет уровня модуляции (количество единиц в наборе 28 семплов). 20/28 (20 единиц из выборки 28) соответствует +3.10 dB SA-CD - это максимально разрешенное значение.

При его превышении - рапортует о клиппинге.

Делать?

А я бы, кстати, наоборот, небольшую асимметрию по плечам ввел. Чтобы вторая гармоника не компенсировалась и была больше третьей хотя бы на 5-6дБ.

Может быть, кстати, это еще и питанием можно регулировать.

Читаешь мои мысли.

Не понятна прикладная нагрузка и финальная концепция реализации этого проекта в железе / обвязка. По этому пока смысла не вижу…

ответ на твой вопрос содержится в документе:

В классической схеме реализации DSC (сдвиговые регистры) – улучшить точность уровня можно только увеличивая точность всех резисторов. Эффект влияния n на точность восстановления уровня сохраниться.

Схема, предложенная insert:

[…]

- Можно добиться увеличения точности восстановления путем использования

высокоточных резисторов для первых и последних 5-6 резисторов в наборе из 32

установив резисторы, например, с точностью 0,01%.

IMO:

- экспериментировать с количеством резюков точно стоит, но в большую сторону 32, 36, 40 … Это давняя мечта, мы эту тему с Алексеем давно обсуждали. Если использовать большое количество резисторов в плече - улучшиться точность установления уровней даже без использования 0,01% резисторов. Да и импеданс выходной уменьшить можно (если нужно).

- Да, если пожертвовать изолятором. Т.е. flip-flop на выходе FPGA - и убрать внешние flip-flop. У Soekris так сделано.

- Не нужно, Это только для измерения уровня громкости необходимо. Даже если уровень модуляции выше стандарта (очевидно есть такие записи) - просто будет хуже точность установления уровня при высоких уровнях модуляции. С исследовательской точки зрения можно считать уровень модуляции и выводить его для отображения. Так можно будет понять, с какими уровнями модуляции DSС обычно работает.

Алексей, я на сейчас очень плохо в этом разбираюсь. Надеюсь, что эксперименты в ближайшую неделю добавят понимания - тогда можно будет что то осмысленное написать.

Окончательно прочли мои мысли  .

.

При чем с CPLD это делается в 2 счета. Только плат понадобится в 2 раза больше(для баланса).

Если баланс не нужен (смещение 2,5В для лампы), то можно обойтись 1 платой.

DSC как раз хорош своей простотой

На мой взгляд, экспериментировать надо прежде всего с формой окна FIR - фильтра.

Это очень хлопотно с точки зрения подбора резисторов, но разрешение по уровню по идее должно возрасти кардинально.

И схема с не прямоугольной формой окна будет корректно работать только с токовым выходом.

Я думаю что правильнее даже устанавливать “шириину FIR” необходимо в зависимости от скорости потока DSD. НАпример для 512 брать 56 - 64 бита…

_п.с. ох ребята, столько новых идей приходит по концепции DSC/// Но надо все по порядку, благо будет ПЛИС и будет погибше крутилки крутить. Вот оно, поле для разбега

_